LAPRAK MODUL 3 PERCOBAAN 1

3. Rangkaian Simulasi[Kembali]

4. Prinsip Kerja Rangkaian[Kembali]

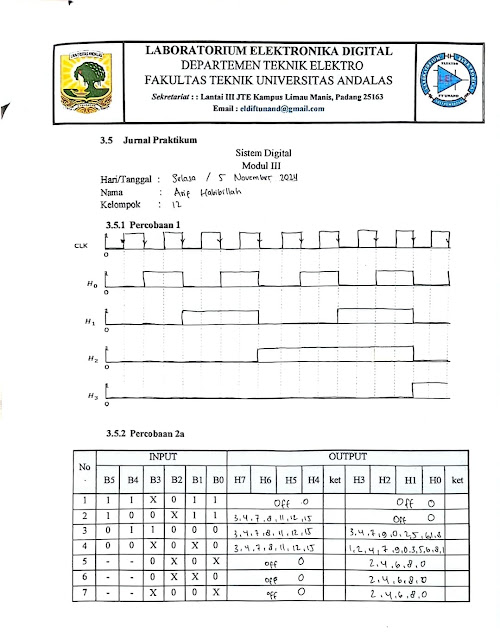

Pada percobaan 1 digunakan Asynchronous Binary Counter 4 bit dengan 4 buah J-K flip flop. Jika input T- flip flop (input J dan K yang disatukan) pada JK flip flop dihubung ke power, maka output IC akan mengalami kondisi toogle. Tetapi, jika JK flip flop input clock yang dihubungkan clock maka output toogle pada masing-masing IC akan berubah sesuai dengan keadaan aktifnya, yaitu aktif saat fall time.

Jika clock dalam kondisi fall time, maka output flip flop pertama akan berubah outputnya menjadi 1, sedangkan pada flip flop kedua tidak terpengaruh apapun karena input clock kedua diperoleh dari output flip flop pertama. Akibatnya, clock flip flop kedua dalam kondisi rise time sehingga outputnya adalah 0. Begitupun seterusnya pada ke tiga dan ke empat sehingga diperoleh outputnya secara bergiliran dan bergantian mengalami kenaikan atau penurunan pada outputnya.

Video Percobaan

Komentar

Posting Komentar