LAPRAK MODUL 2 PERCOBAAN 2

3. Rangkaian Simulasi[Kembali]\

- Rangkaian 1

- Rangkaian 2

4. Prinsip Kerja Rangkaian[Kembali]

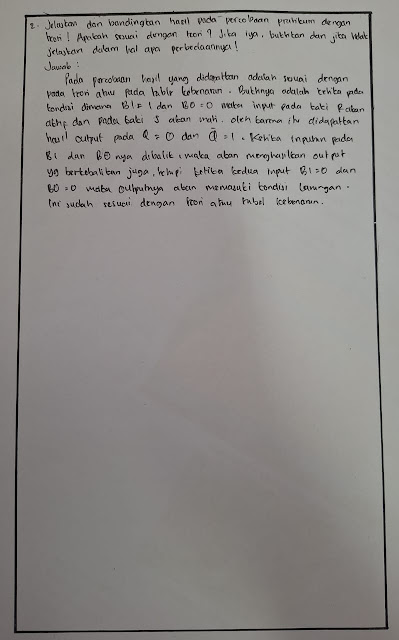

D Flip-Flop, atau sering disebut sebagai Data atau Delay Flip-Flop, adalah salah satu jenis flip-flop yang lebih sederhana. D Flip-Flop hanya memiliki satu input utama, yaitu D (Data), dan biasanya digunakan untuk menyimpan satu bit data pada tepi naik clock. Flip-flop ini mengatasi kelemahan flip-flop lainnya yang memiliki dua input yang lebih kompleks, dengan merampingkannya menjadi satu input saja.

-Ketika clock dalam keadaan tidak aktif (misalnya clock rendah atau sebelum mencapai tepi naik), output Q akan tetap mempertahankan nilai sebelumnya. Dengan kata lain, perubahan input D tidak akan mempengaruhi output selama clock tidak aktif.

-Ketika clock dalam keadaan aktif (biasanya tepi naik clock), nilai dari input D akan diteruskan ke output Q. Jika D adalah "1", maka Q akan menjadi "1". Jika D adalah "0", maka Q akan menjadi "0". Dengan demikian, output hanya berubah berdasarkan nilai input D pada saat clock aktif.

-D Flip-Flop sering digunakan sebagai penyimpanan data atau register, karena perilaku input D yang sederhana. Input D secara langsung menentukan nilai output, dan output akan tetap stabil sampai clock aktif kembali untuk mengambil nilai baru dari input D.

.png)

.png)

.png)

.png)

Komentar

Posting Komentar